Titan

Titan II | |

| Designed By | IBM |

|---|---|

The Titan is a development board used during bringup of the Shiva and Waternoose Engineering Sample CPUs. It also allows an IBM RISCWatch to be used to debug and test the processors.

Specifications

- Xilinx Spartan 3 XC3S200 FPGA

- 128KB Xilinx XCF01S JTAG PROM

- 4 DIP Switches

- 9 3.3V LEDs (Titan II only)

- 50MHz 3.3V Crystal

Details

There are two versions, the Titan and the Titan II.

The Titan is powered off the console via the 3.3V V_MEMPORT and 1.8V V_1P8 rails. The 3.3V is also stepped down to 2.5V and 1.2V.

The 10-pin J_YETI header connects to J8C1, the CPU JTAG header, while the 12-pin J_GPUL header connects to J7G2, the Shiva GPUL JTAG header.

Different bitstreams are required for Shiva, and the various revisions of Waternoose, due to difference in Power On Reset.

The DIP switch operation is not currently known. The recommended configuration is OFF - OFF - ON - OFF.

LEDs

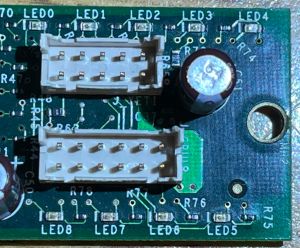

The Titan II has 9 LEDs mounted near one end. Reverse engineering has been used to determine their meaning. Earlier Titan revisions do not have LEDs, as the GPIOs that control them are connected to the J_GPUL header for connecting to Shiva.

- LED 0 through LED 4 are blue LEDs that indicate the status code between 0x00 and 0x1F. Bit 0 (LED 0) is MSB.

For DD1 Firmware:

- LED 5 is a red LED that indicates when the Titan times out when attempting to boot the CPU.

- LED 6 is a green LED that indicates booting priority is Secure ROM.

- LED 7 is a yellow LED that indicates booting priority is Sysver.

- LED 8 is a red LED that indicates that the cores will be held for RISCWatch use.

Gallery