Titan: Difference between revisions

No edit summary |

|||

| (43 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{Infobox Chip | {{Infobox Chip | ||

| name = Titan | | name = Titan | ||

| image = Titan | | image = Titan.jpg | ||

| image_size = 350px | | image_size = 350px | ||

| caption = Titan II | | caption = Titan | ||

| image2 = Titan-II.jpg | |||

| caption2 = Titan II | |||

| designedby = IBM | | designedby = IBM | ||

}} | }} | ||

'''Titan''' is a development/test card used during bringup of the [[Shiva]] and [[Waternoose]] Engineering Sample CPUs. It also allows an IBM RISCWatch to be used to debug and test the processors. | |||

== Specifications == | |||

* Xilinx Spartan 3 XC3S200 FPGA | |||

* 128KB Xilinx XCF01S JTAG PROM | |||

* 4 DIP Switches | |||

* 9 3.3V LEDs (Titan II only) | |||

* 50MHz 3.3V Crystal | |||

== Details == | |||

There are two versions, the Titan and the Titan II. Titan was original designed as the service processor for [[Shiva]], as PowerPC 970 series required one to start up. | |||

Due to mistakes in [[Waternoose#DD1|Waternoose DD1]], Titan continued to be used until [[Waternoose#DD2|Waternoose DD2]] was available. From then on, it was only used for RISCWatch debugging connectivity. | |||

Titan can be plugged into any [[Original Xbox 360]] [[motherboards]] with J7G2/J7G3 headers. This excludes final motherboards, unless modifications are performed. However, it must only be used on [[Waternoose]] CPUs. Damage will occur if attempting to use Titan on Loki, as no Loki-compatible firmware is known to exist. | |||

Primary Titan power is provided by the console via the 3.3V [[Power Rails (Original)#V_MPORT|V_MPORT]]. This is stepped down to 2.5V and 1.2V. | |||

Additional I/O voltage is provided by the console. When used on [[Shiva]], Titan receives 1.3V from [[Power Rails (Original)#V_CPUCORE|V_CPUCORE]]. On [[Waternoose]], it receives 1.8V from [[Power Rails (Original)#V_1P8|V_1P8]]. Titan requires this 1.8V on J_GPUL, while Titan-II requires it on J_YETI. | |||

The 10-pin J_YETI header connects to J8C1, the CPU JTAG header, while the 12-pin J_GPUL header connects to J7G2, the [[Shiva]] GPUL JTAG header. Shiva firmware and very early [[Waternoose#DD1|Waternoose DD1]] firmware require J8C1 pin 2 to be connected to the 1.8V CPU_RST_N signal instead of the 1.1V CPU_RST_V1P1_N signal. | |||

Different bitstreams are required for Shiva, and the various revisions of Waternoose, due to difference in [[Power On Reset]]. | |||

The some of the DIP switches are specific to the firmware version. | |||

=== Switches === | |||

Titan has 4 switches which are connected to the FPGA. They are used to modify [[Power On Reset]] behavior. Switch behavior varies depending on the firmware version. | |||

Recommended configurations: | |||

Where VREF is listed, switch should be ON if GPU is A21N2 or newer, and off if GPU is A21N1 or older. This switch controls Titan usage of GPU VREF bandgap. | |||

{|class="wikitable" | |||

! Hex !! Description | |||

|- | |||

| Shiva || To be determined | |||

|- | |||

| DD1 v0.8 || OFF - OFF - ON - OFF | |||

|- | |||

| DD1 v1.7 || OFF - OFF - ON - OFF | |||

|- | |||

| DD1 v2.11 || OFF - OFF - VREF - OFF | |||

|- | |||

| DD1 v2.17 || OFF - OFF - VREF - OFF | |||

|- | |||

| DD2 v11 || ON - OFF - VREF - OFF | |||

|} | |||

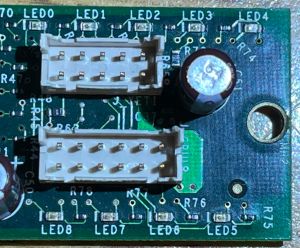

=== LEDs === | |||

The Titan II has 9 LEDs mounted near one end. Reverse engineering has been used to determine their meaning. Earlier Titan revisions do not have LEDs, as the GPIOs that control them are connected to the J_GPUL header for [[Shiva]]. As a result, Titan II boards cannot use Shiva firmware. | |||

For DD1 Firmware: | |||

* LED 0 through LED 4 are blue LEDs that indicate the status code between 0x00 and 0x1F. Bit 0 (LED 0) is the most significant bit. | |||

* LED 5 is a red LED that indicates when the Titan times out when attempting to boot the CPU. | |||

* LED 6 is a green LED that indicates booting priority is [[Secure ROM]]. | |||

* LED 7 is a yellow LED that indicates booting priority is [[Sysver]]. | |||

* LED 8 is a red LED that indicates that the cores will be held for [[RISCWatch]] use. | |||

<gallery widths=300px heights=248px> | |||

File:Titan-II-LEDs.jpg | |||

</gallery> | |||

=== Status Codes (WN) === | |||

For [[Waternoose]] firmwares, Titan outputs a status code during the boot process. For Titan, this code can be found by probing pins 1, 3, 5, 7, 9 of J_GPUL. For Titan-II, this code is displayed on LEDs 0-4. | |||

Starting with firmware V1.7/V2.7, the polarity of the bits was inverted, likely to support the LED circuits for Titan-II. Very early firmware versions do not have this status code. | |||

The following status codes have been discovered using reverse engineering. Reminder that when probing for bits, the polarity must be inverted. | |||

[[Waternoose#DD1|Waternoose DD1]] CPUs with Glitchless-mux or AVDD issues will fail Titan at 0x05. | |||

Titan-II on V2.12 or later will flash 0x1D if the FSB communication is flakey. | |||

Titan-II on V2.13 or later will flash 0x1F if the CPU checkstops. | |||

Titan-II on V2.13 or later will display a knight rider light pattern when Titan completes. | |||

{|class="wikitable" | |||

! Hex !! Description | |||

|- | |||

| 0x00 || Waiting for JTAG | |||

|- | |||

| 0x05 || Apply VID, ramp clocks | |||

|- | |||

| 0x16 || Soft reset | |||

|- | |||

| 0x17 || FSB not trained | |||

|- | |||

| 0x1B || FSB test failed | |||

|- | |||

| 0x1C || FSB test passed | |||

|- | |||

| 0x1F || FSB trained, Titan complete | |||

|} | |||

== Gallery == | |||

<gallery widths=500px heights=261px> | <gallery widths=500px heights=261px> | ||

File:XeDK-007-1.jpg| | File:XeDK-007-1.jpg|Xenon 007 with Titan II powered on | ||

</gallery> | </gallery> | ||

[[Category:Console Components]] | |||

{{Console Components}} | |||

Latest revision as of 00:40, 9 August 2024

Titan | |

Titan II | |

| Designed By | IBM |

|---|---|

Titan is a development/test card used during bringup of the Shiva and Waternoose Engineering Sample CPUs. It also allows an IBM RISCWatch to be used to debug and test the processors.

Specifications

- Xilinx Spartan 3 XC3S200 FPGA

- 128KB Xilinx XCF01S JTAG PROM

- 4 DIP Switches

- 9 3.3V LEDs (Titan II only)

- 50MHz 3.3V Crystal

Details

There are two versions, the Titan and the Titan II. Titan was original designed as the service processor for Shiva, as PowerPC 970 series required one to start up.

Due to mistakes in Waternoose DD1, Titan continued to be used until Waternoose DD2 was available. From then on, it was only used for RISCWatch debugging connectivity.

Titan can be plugged into any Original Xbox 360 motherboards with J7G2/J7G3 headers. This excludes final motherboards, unless modifications are performed. However, it must only be used on Waternoose CPUs. Damage will occur if attempting to use Titan on Loki, as no Loki-compatible firmware is known to exist.

Primary Titan power is provided by the console via the 3.3V V_MPORT. This is stepped down to 2.5V and 1.2V.

Additional I/O voltage is provided by the console. When used on Shiva, Titan receives 1.3V from V_CPUCORE. On Waternoose, it receives 1.8V from V_1P8. Titan requires this 1.8V on J_GPUL, while Titan-II requires it on J_YETI.

The 10-pin J_YETI header connects to J8C1, the CPU JTAG header, while the 12-pin J_GPUL header connects to J7G2, the Shiva GPUL JTAG header. Shiva firmware and very early Waternoose DD1 firmware require J8C1 pin 2 to be connected to the 1.8V CPU_RST_N signal instead of the 1.1V CPU_RST_V1P1_N signal.

Different bitstreams are required for Shiva, and the various revisions of Waternoose, due to difference in Power On Reset.

The some of the DIP switches are specific to the firmware version.

Switches

Titan has 4 switches which are connected to the FPGA. They are used to modify Power On Reset behavior. Switch behavior varies depending on the firmware version.

Recommended configurations:

Where VREF is listed, switch should be ON if GPU is A21N2 or newer, and off if GPU is A21N1 or older. This switch controls Titan usage of GPU VREF bandgap.

| Hex | Description |

|---|---|

| Shiva | To be determined |

| DD1 v0.8 | OFF - OFF - ON - OFF |

| DD1 v1.7 | OFF - OFF - ON - OFF |

| DD1 v2.11 | OFF - OFF - VREF - OFF |

| DD1 v2.17 | OFF - OFF - VREF - OFF |

| DD2 v11 | ON - OFF - VREF - OFF |

LEDs

The Titan II has 9 LEDs mounted near one end. Reverse engineering has been used to determine their meaning. Earlier Titan revisions do not have LEDs, as the GPIOs that control them are connected to the J_GPUL header for Shiva. As a result, Titan II boards cannot use Shiva firmware.

For DD1 Firmware:

- LED 0 through LED 4 are blue LEDs that indicate the status code between 0x00 and 0x1F. Bit 0 (LED 0) is the most significant bit.

- LED 5 is a red LED that indicates when the Titan times out when attempting to boot the CPU.

- LED 6 is a green LED that indicates booting priority is Secure ROM.

- LED 7 is a yellow LED that indicates booting priority is Sysver.

- LED 8 is a red LED that indicates that the cores will be held for RISCWatch use.

Status Codes (WN)

For Waternoose firmwares, Titan outputs a status code during the boot process. For Titan, this code can be found by probing pins 1, 3, 5, 7, 9 of J_GPUL. For Titan-II, this code is displayed on LEDs 0-4.

Starting with firmware V1.7/V2.7, the polarity of the bits was inverted, likely to support the LED circuits for Titan-II. Very early firmware versions do not have this status code.

The following status codes have been discovered using reverse engineering. Reminder that when probing for bits, the polarity must be inverted.

Waternoose DD1 CPUs with Glitchless-mux or AVDD issues will fail Titan at 0x05.

Titan-II on V2.12 or later will flash 0x1D if the FSB communication is flakey.

Titan-II on V2.13 or later will flash 0x1F if the CPU checkstops.

Titan-II on V2.13 or later will display a knight rider light pattern when Titan completes.

| Hex | Description |

|---|---|

| 0x00 | Waiting for JTAG |

| 0x05 | Apply VID, ramp clocks |

| 0x16 | Soft reset |

| 0x17 | FSB not trained |

| 0x1B | FSB test failed |

| 0x1C | FSB test passed |

| 0x1F | FSB trained, Titan complete |

Gallery